ほとんど生成AIで作るFPGA開発(PDF版)

- ダウンロード商品¥ 1,000

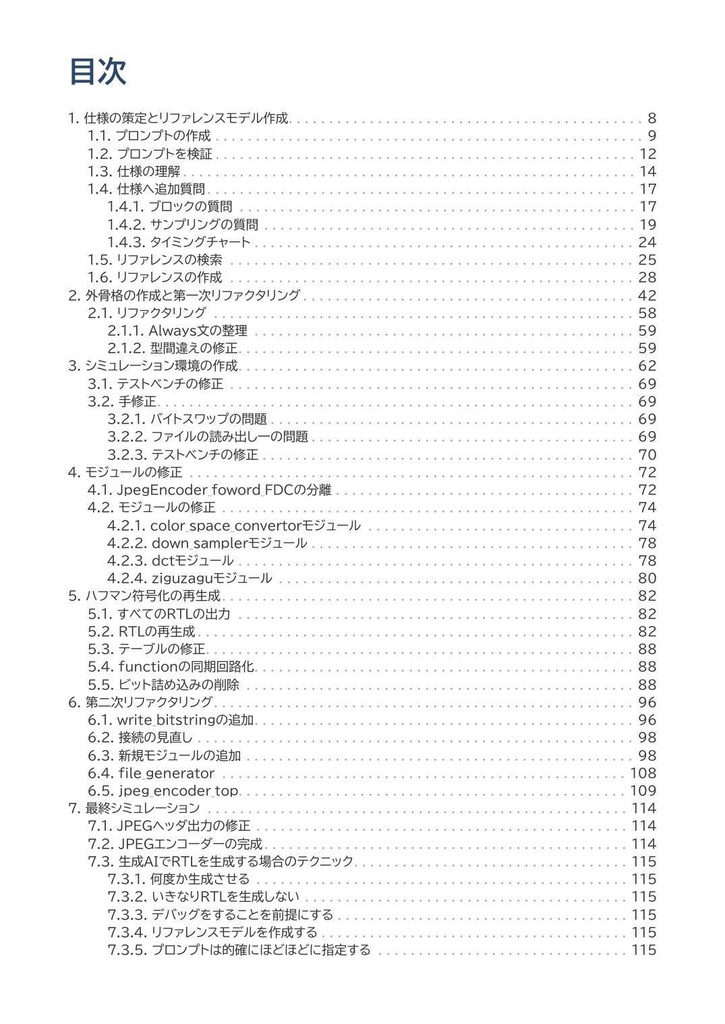

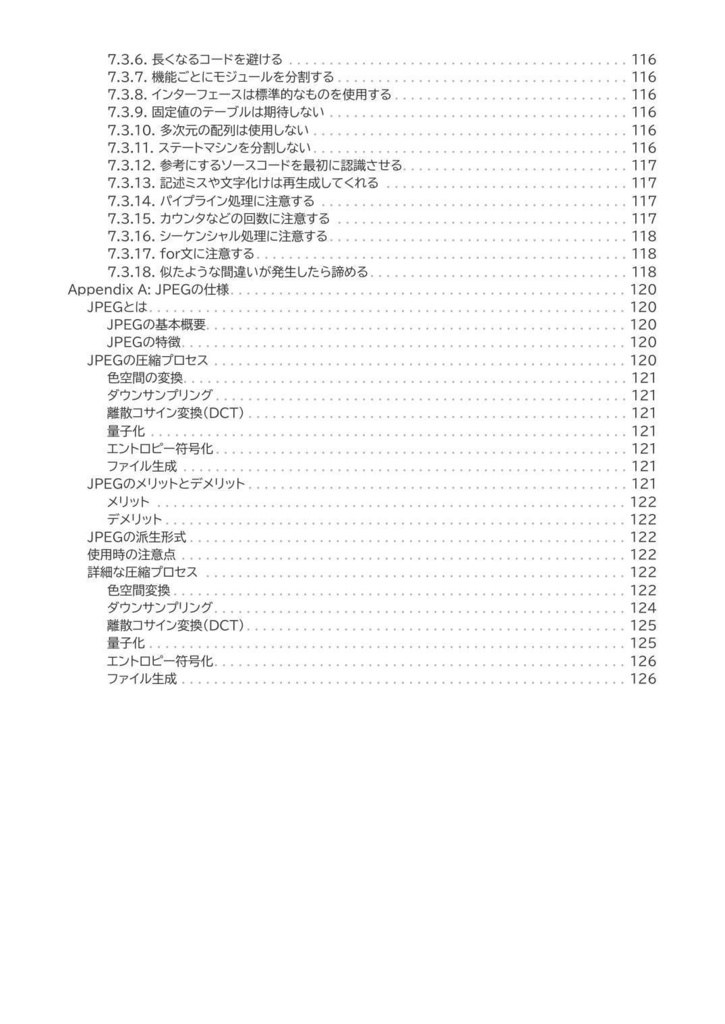

「ほとんど生成AIで作るFPGA開発」(FPGAの薄い本シリーズ9) B5/132p/技術書典18/2025年6月発行 SystemVerilogのRTLをほとんど生成AIで書かせてしまう内容です。 どのようなプロンプトを与えてうまく生成しているかJPEGエンコーダーの作成を実例に上げて解説します。 1. 仕様の策定とリファレンスモデル作成 1.1. プロンプトの作成 1.2. プロンプトを検証 1.3. 仕様の理解 1.4. 仕様へ追加質問 1.4.1. ブロックの質問 1.4.2. サンプリングの質問 1.4.3. タイミングチャート 1.5. リファレンスの検索 1.6. リファレンスの作成 2. 外骨格の作成と第一次リファクタリング 2.1. リファクタリング 2.1.1. Always文の整理 2.1.2. 型間違えの修正 3. シミュレーション環境の作成 3.1. テストベンチの修正 3.2. 手修正 3.2.1. バイトスワップの問題 3.2.2. ファイルの読み出し一の問題 3.2.3. テストベンチの修正 4. モジュールの修正 4.1. JpegEncoder_foword_FDCの分離 4.2. モジュールの修正 4.2.1. color_space_convertorモジュール 4.2.2. down_samplerモジュール 4.2.3. dctモジュール 4.2.4. ziguzaguモジュール 5. ハフマン符号化の再生成 5.1. すべてのRTLの出力 5.2. RTLの再生成 5.3. テーブルの修正 5.4. functionの同期回路化 5.5. ビット詰め込みの削除 6. 第二次リファクタリング 6.1. write_bitstringの追加 6.2. 接続の見直し 6.3. 新規モジュールの追加 6.4. file_generator 6.5. jpeg_encoder_top 7. 最終シミュレーション 7.1. JPEGヘッダ出力の修正 7.2. JPEGエンコーダーの完成 7.3. 生成AIでRTLを生成する場合のテクニック 7.3.1. 何度か生成させる 7.3.2. いきなりRTLを生成しない 7.3.3. デバッグをすることを前提にする 7.3.4. リファレンスモデルを作成する 7.3.5. プロンプトは的確にほどほどに指定する 7.3.6. 長くなるコードを避ける 7.3.7. 機能ごとにモジュールを分割する 7.3.8. インターフェースは標準的なものを使用する 7.3.9. 固定値のテーブルは期待しない 7.3.10. 多次元の配列は使用しない 7.3.11. ステートマシンを分割しない 7.3.12. 参考にするソースコードを最初に認識させる 7.3.13. 記述ミスや文字化けは再生成してくれる 7.3.14. パイプライン処理に注意する 7.3.15. カウンタなどの回数に注意する 7.3.16. シーケンシャル処理に注意する 7.3.17. for文に注意する 7.3.18. 似たような間違いが発生したら諦める Appendix A: JPEGの仕様