AIでSystemVerilogを書く技術(物理本+PDF本、PDF本)

- 物理本+PDF本Ships within 4 daysPhysical (direct)1,600 JPY

- PDF版Digital1,000 JPY

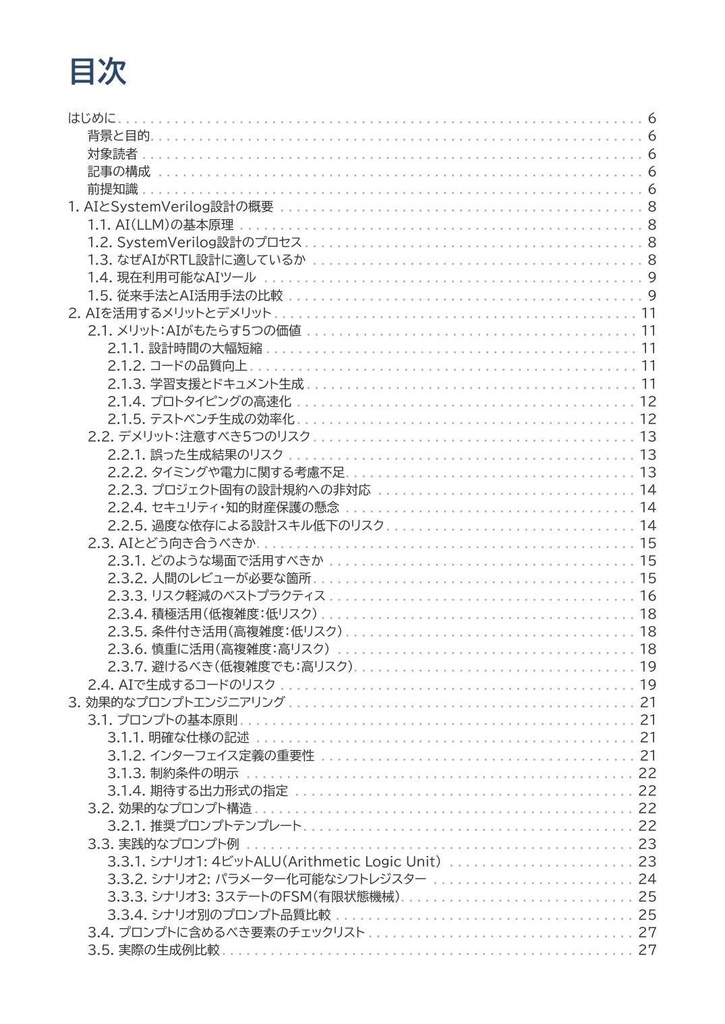

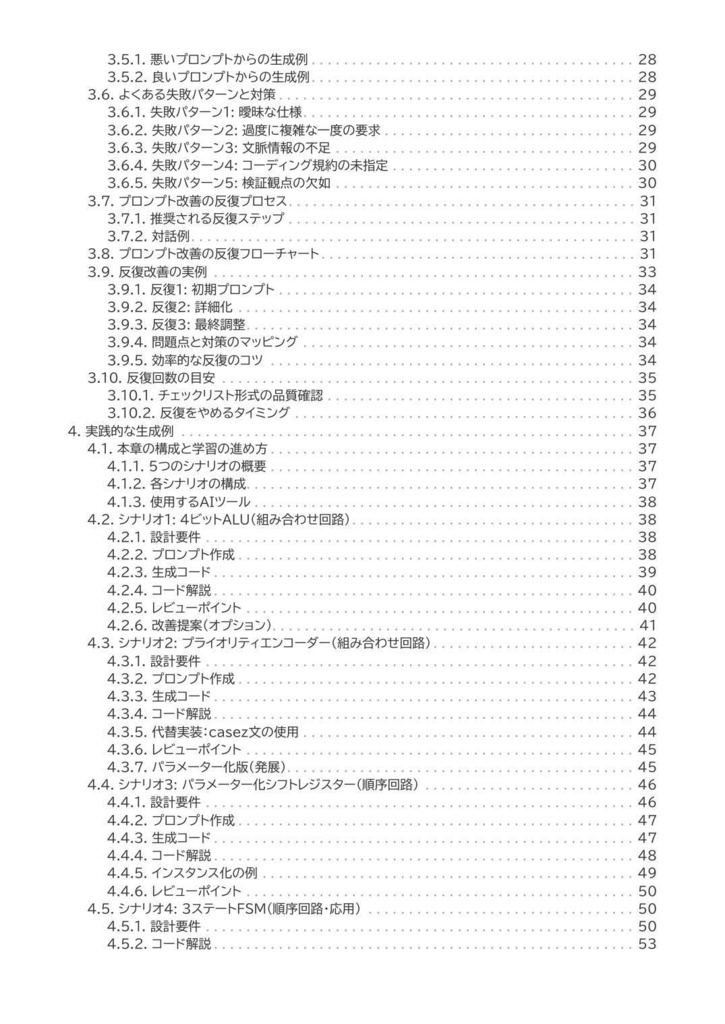

「AIでSystemVerilogを書く技術」(FPGAの薄い本シリーズ10) B5/100p/技術書典19/2025年11月発行 AIを使用してSystemVerilogでRTLを書く基礎編をまとめた1冊です。 1. AIとSystemVerilog設計の概要 1.1. AI(LLM)の基本原理 1.2. SystemVerilog設計のプロセス 1.3. なぜAIがRTL設計に適しているか 1.4. 現在利用可能なAIツール 1.5. 従来手法とAI活用手法の比較 2. AIを活用するメリットとデメリット 2.1. メリット:AIがもたらす5つの価値 2.1.1. 設計時間の大幅短縮 2.1.2. コードの品質向上 2.1.3. 学習支援とドキュメント生成 2.1.4. プロトタイピングの高速化 2.1.5. テストベンチ生成の効率化 2.2. デメリット:注意すべき5つのリスク 2.2.1. 誤った生成結果のリスク 2.2.2. タイミングや電力に関する考慮不足. 2.2.3. プロジェクト固有の設計規約への非対応 2.2.4. セキュリティ・知的財産保護の懸念 2.2.5. 過度な依存による設計スキル低下のリスク 2.3. AIとどう向き合うべきか. 2.3.1. どのような場面で活用すべきか 2.3.2. 人間のレビューが必要な箇所. 2.3.3. リスク軽減のベストプラクティス 2.3.4. 積極活用(低複雑度:低リスク) 2.3.5. 条件付き活用(高複雑度:低リスク) 2.3.6. 慎重に活用(高複雑度:高リスク) 2.3.7. 避けるべき(低複雑度でも:高リスク). 2.4. AIで生成するコードのリスク 3. 効果的なプロンプトエンジニアリング 3.1. プロンプトの基本原則. 3.1.1. 明確な仕様の記述 3.1.2. インターフェイス定義の重要性 3.1.3. 制約条件の明示 3.1.4. 期待する出力形式の指定 3.2. 効果的なプロンプト構造 3.2.1. 推奨プロンプトテンプレート. 3.3. 実践的なプロンプト例 3.3.1. シナリオ1: 4ビットALU(Arithmetic Logic Unit) 3.3.2. シナリオ2: パラメーター化可能なシフトレジスター 3.3.3. シナリオ3: 3ステートのFSM(有限状態機械). 3.3.4. シナリオ別のプロンプト品質比較 3.4. プロンプトに含めるべき要素のチェックリスト 3.5. 実際の生成例比較 3.5.1. 悪いプロンプトからの生成例 3.5.2. 良いプロンプトからの生成例. 3.6. よくある失敗パターンと対策 3.6.1. 失敗パターン1: 曖昧な仕様. 3.6.2. 失敗パターン2: 過度に複雑な一度の要求 3.6.3. 失敗パターン3: 文脈情報の不足 3.6.4. 失敗パターン4: コーディング規約の未指定 3.6.5. 失敗パターン5: 検証観点の欠如 3.7. プロンプト改善の反復プロセス. 3.7.1. 推奨される反復ステップ 3.7.2. 対話例. 3.8. プロンプト改善の反復フローチャート 3.9. 反復改善の実例 3.9.1. 反復1: 初期プロンプト 3.9.2. 反復2: 詳細化 3.9.3. 反復3: 最終調整. 3.9.4. 問題点と対策のマッピング 3.9.5. 効率的な反復のコツ 3.10. 反復回数の目安 3.10.1. チェックリスト形式の品質確認 3.10.2. 反復をやめるタイミング 4. 実践的な生成例 4.1. 本章の構成と学習の進め方 4.1.1. 5つのシナリオの概要 4.1.2. 各シナリオの構成. 4.1.3. 使用するAIツール 4.2. シナリオ1: 4ビットALU(組み合わせ回路) 4.2.1. 設計要件 4.2.2. プロンプト作成 4.2.3. 生成コード 4.2.4. コード解説 4.2.5. レビューポイント 4.2.6. 改善提案(オプション). 4.3. シナリオ2: プライオリティエンコーダー(組み合わせ回路) 4.3.1. 設計要件 4.3.2. プロンプト作成 4.3.3. 生成コード 4.3.4. コード解説 4.3.5. 代替実装:casez文の使用 4.3.6. レビューポイント 4.3.7. パラメーター化版(発展). 4.4. シナリオ3: パラメーター化シフトレジスター(順序回路) 4.4.1. 設計要件 4.4.2. プロンプト作成 4.4.3. 生成コード 4.4.4. コード解説 4.4.5. インスタンス化の例 4.4.6. レビューポイント 4.5. シナリオ4: 3ステートFSM(順序回路・応用) 4.5.1. 設計要件 4.5.2. コード解説 4.5.3. FSMの設計パターン 4.5.4. レビューポイント 4.5.5. シナリオ4のポイント 4.6. シナリオ5: FIFOバッファー(複雑なモジュール) 4.6.1. 設計要件 4.6.2. プロンプト作成 4.6.3. 生成コード 4.6.4. コード解説 4.6.5. 代替実装:グレイコードポインター 4.6.6. レビューポイント 4.6.7. AIの限界と人間の補完. 4.6.8. シナリオ5のポイント. 4.7. シナリオ別の難易度と生成品質マトリクス. 4.7.1. 詳細分析表. 5. AIコーディングエージェントの活用 5.1. 主要AIコーディングエージェントの分類 5.1.1. チャット型AI(対話型). 5.1.2. IDE統合型(リアルタイム補完型) 5.1.3. プロジェクト型エージェント(ファイル横断型) 5.2. ツール別の詳細比較 5.3. タスク別の推奨ツール 5.3.1. 設計フェーズ別の推奨 5.3.2. モジュール複雑度別の推奨 5.4. 実践的な活用ワークフロー 5.4.1. 具体的な作業例 5.5. フェーズ別詳細ワークフロー 5.5.1. フェーズ1: 設計検討(チャット型AI活用) 5.5.2. フェーズ2: 初期実装(チャット型AI活用) 5.5.3. フェーズ3: 実装補完(IDE統合型活用). 5.5.4. フェーズ4: 統合・改善(プロジェクト型活用). 6. AIの苦手領域と対処法. 6.1. AIが苦手とする設計領域 6.2. フェーズ別AI活用度 6.3. 苦手領域の具体例 6.3.1. タイミング制約が厳しい設計 6.3.2. クロックドメインクロッシング(CDC) 6.3.3. 低消費電力設計 6.3.4. 大規模モジュールの統合. 6.3.5. プロジェクト固有の設計規約 6.3.6. アナログ/ミックスドシグナル設計 6.4. 検証が必須の項目 6.4.1. 文法チェック(リントツール) 6.4.2. 論理シミュレーション 6.4.3. 形式検証 6.4.4. タイミング解析 6.4.5. CDC検証 6.5. ハイブリッドアプローチのベストプラクティス. 6.6. 役割分担の詳細 6.7. フェーズ別詳細フロー 6.8. 複雑度別のハイブリッドアプローチ 6.8.1. シンプルなモジュール(★~★★) 6.8.2. 中規模モジュール(★★★) 6.8.3. 複雑なモジュール(★★★★~★★★★★) 6.9. ハイブリッドアプローチの原則 6.10. 推奨ワークフロー 6.11. リスク軽減のチェックリスト 6.11.1. 設計フェーズ. 6.11.2. 実装フェーズ. 6.11.3. 検証フェーズ. 6.11.4. レビューフェーズ 6.12. よくある失敗パターンと対策 6.12.1. 失敗パターン1: 生成コードを盲目的に信頼 6.12.2. 失敗パターン2: タイミング制約を後回し 6.12.3. 失敗パターン3: プロジェクト規約の無視 6.12.4. 失敗パターン4: 複雑すぎる一度の要求. 6.12.5. 失敗パターン5: テストベンチの省略 6.13. 成功の鍵となる5つのポイント